Xilinx ise 14.6 add a bus

- #XILINX ISE 14.6 ADD A BUS MANUALS#

- #XILINX ISE 14.6 ADD A BUS GENERATOR#

- #XILINX ISE 14.6 ADD A BUS FULL#

#XILINX ISE 14.6 ADD A BUS FULL#

A full 1-bit adder (from now on, sum1 ) is a logic circuit that adds three bits ("A", "B" and "Ci", where "A" and "B" are the source bits and "Ci" ("i" from "input") is the input carry bit from a previous add stage) and produces the add bit "S" and the output carry bit "Co" ("o" from "out"). 3Ĥ Tutorial: Introduction to FPGA design with Xilinx ISE 13 and prototyping boards. These resources will be provided by the instructor.

#XILINX ISE 14.6 ADD A BUS MANUALS#

Some source files, manuals and documents are required along this tutorial.

The used FPGA must have libraries with the common elements used in this lab Sources and documents. Using other prototyping boards: This lab can be easily adapted to be used with other prototyping boards, if the following issues are taken into account: The I/O FPGA pins must be correctly mapped to the DIP and LED devices in the board.

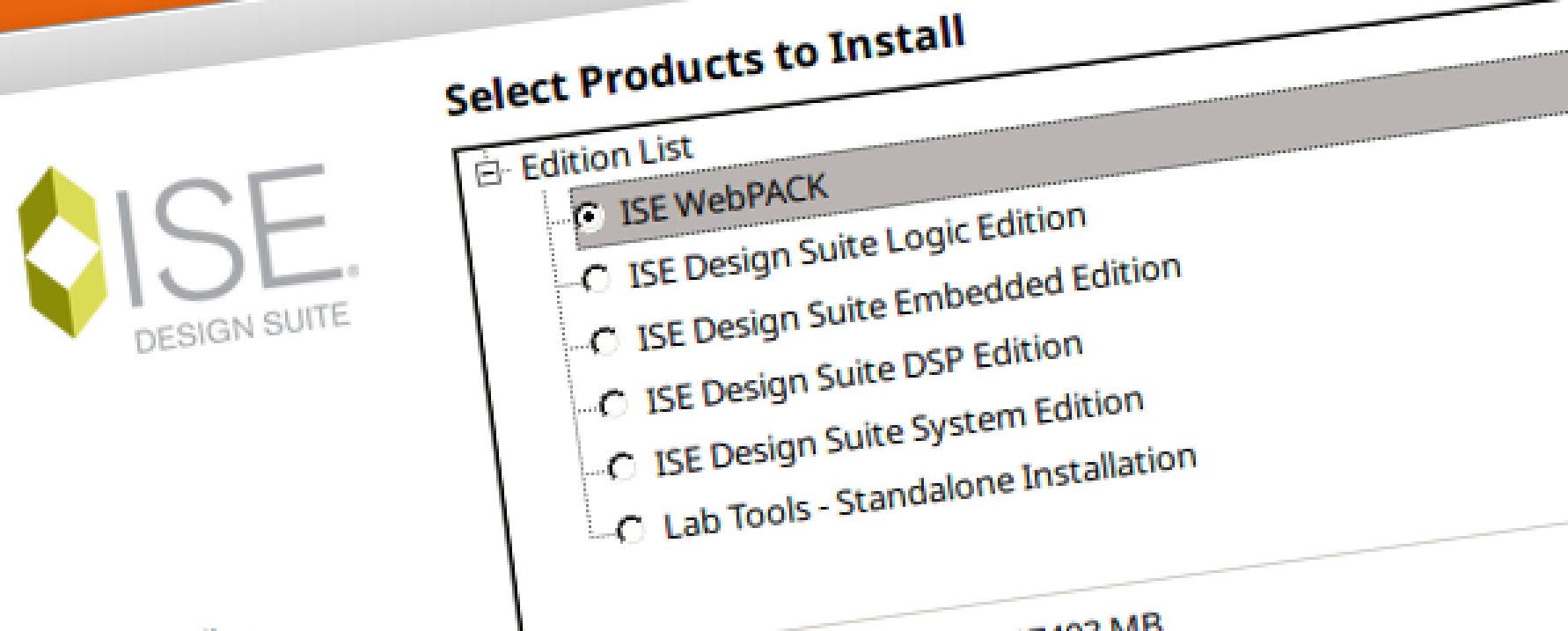

A prototyping board: Digilent Nexys, Nexys2. Xilinx PicoBlaze for Spartan3 libraries and software. Considerations: All variable names will be displayed within quotation marks ( ) Tools. The following steps implement the typical phases of the design cycle: idea, modeling, simulation, synthesis and implementation, time analysis, prototyping and debugging.

This lab introduces the student in the use of tools and platforms for reconfigurable computing.

#XILINX ISE 14.6 ADD A BUS GENERATOR#

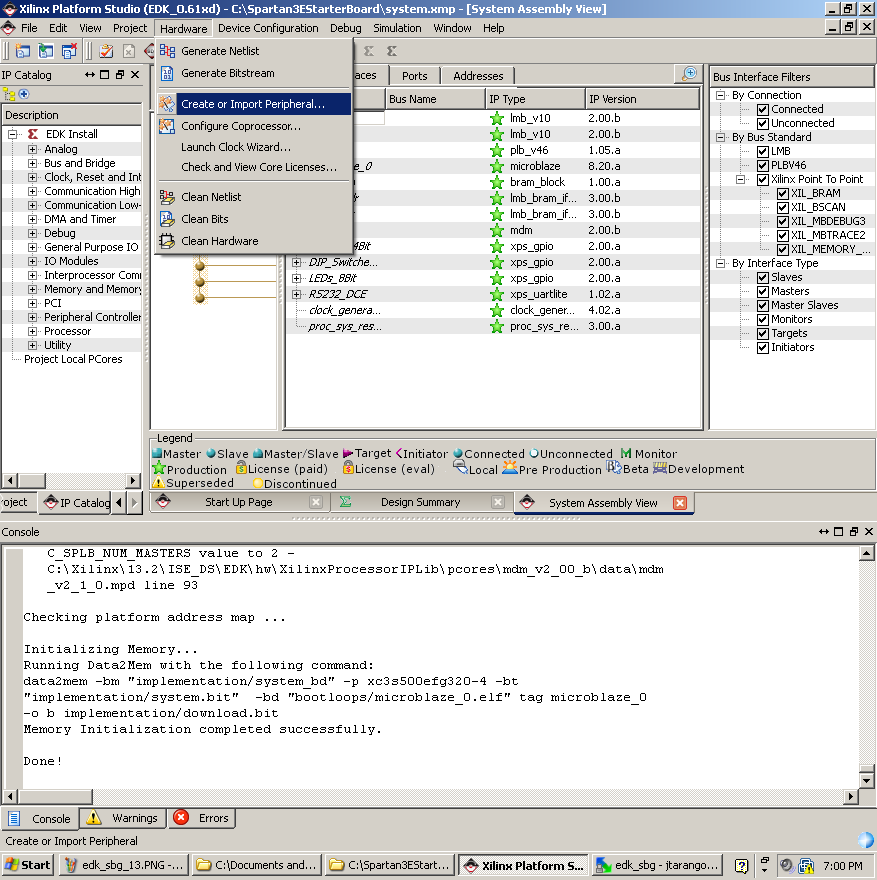

Introduction Purpose Tools Sources and documents System design Modeling a 1-bit adder Creating the project sumacon Creating the sum1 object by means of schematic Functional simulation Simulating using VHDL Test Bench Modeling and functional simulation of an 8-bit adder Creating the sum1 symbol Creating the 8-bit adder Counter modelled from Core Generator Implementation Preparing the circuit Introduction Planning the system Buses connector Building the memories Decoding the sum Using the 7-segment display Final circuit Implementation and test Assigning FPGA pins Assigning pins in the schematic sheet Assigning pins by means of the user constraints files (UCF) Implementation FPGA layout Implementation reports Testing the design with the board Other models for the system Counter designed from flip-flops Counter modeled from the Picoblaze processor Counter design Final design Implementation Documents General Considerations and Frequently Asked Questions Errores durante la síntesis e implementación Errores en el diseño del proyecto: Nexys / Nexys2 boards Manuals Initial checking FPGA configuration Pins for Nexys Pins for Nexys Clock in Nexysģ 1. Tutorial: Introduction to FPGA design with Xilinx ISE 13 and prototyping boards. Gómez-Pulido Departament of Technologies of Computers and Communications University of Extremadura, Spain (c) 2012 Version: 1/october/2011Ģ Table of contents. 1 Tutorial: Introduction to FPGA design with Xilinx ISE 13 and prototyping boards Juan A.